Delay Fault Testing for VLSI Circuits

ANGELA KRSTIĆ Department of Electrical and Computer Engineering University of California Santa Barbara, CA 93106

KWANG-TING CHENG Department of Electrical and Computer Engineering University of California Santa Barbara, CA 93106

Kluwer Academic Publishers Boston/Dordrecht/London

### Contents

| Pr  | eface                         |                                                                                                                                 | vii     |  |  |

|-----|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Ac  | ix                            |                                                                                                                                 |         |  |  |

| Int | xi                            |                                                                                                                                 |         |  |  |

| An  | Krstić                        |                                                                                                                                 |         |  |  |

| 1.  | TES                           | TEST APPLICATION SCHEMES FOR DELAY FAULTS                                                                                       |         |  |  |

|     | 1.1                           | Combinational Circuits                                                                                                          | 1       |  |  |

|     | 1.2                           | Sequential Circuits                                                                                                             | 2       |  |  |

|     |                               | 1.2.1 Enhanced scan testing                                                                                                     | 3       |  |  |

|     |                               | 1.2.2 Standard scan testing                                                                                                     | 3       |  |  |

|     |                               | 1.2.3 Slow-fast-slow clock testing                                                                                              | 5       |  |  |

|     |                               | 1.2.4 At-speed testing                                                                                                          | 6       |  |  |

|     | 1.3                           | Testing High Performance Circuits Using Slower Testers                                                                          | 6       |  |  |

|     |                               | <ul><li>1.3.1 Slow-fast-slow testing strategy on slow testers</li><li>1.3.2 At-speed testing strategy on slow testers</li></ul> | 8<br>10 |  |  |

|     | C                             |                                                                                                                                 | 10      |  |  |

|     | Sun                           | nmary                                                                                                                           | 14      |  |  |

| 2.  | DEL                           | 15                                                                                                                              |         |  |  |

|     | 2.1                           | 15                                                                                                                              |         |  |  |

|     | 2.2                           | Gate Delay Fault Model                                                                                                          | 18      |  |  |

|     | 2.3                           | Path Delay Fault Model                                                                                                          | 19      |  |  |

|     | 2.4                           | Segment Delay Fault Model                                                                                                       | 21      |  |  |

|     | 2.5                           | Line Delay Fault Model                                                                                                          | 21      |  |  |

|     | Summary                       |                                                                                                                                 |         |  |  |

| 3.  | MOTIVATIONS FOR DELAY TESTING |                                                                                                                                 |         |  |  |

|     | Sum                           | nmary                                                                                                                           | 25      |  |  |

| 4.  | PAT                           | 27                                                                                                                              |         |  |  |

|     | 4.1                           | Sensitization Criteria                                                                                                          | 28      |  |  |

|     |                               | 4.1.1 Robust testable path delay faults                                                                                         | 29      |  |  |

|     |                               | 4.1.2 Non-robust testable path delay faults                                                                                     | 31      |  |  |

|     |                               | 4.1.3 Validatable non-robust testable path delay faults                                                                         | 32      |  |  |

|     |                               | 4.1.4 Functional sensitizable path delay faults                                                                                 | 33      |  |  |

|     |                               |                                                                                                                                 | v       |  |  |

| vi         | DELAY FAULT TESTING FOR VLSI CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|

|            | <ul> <li>4.2 Path Delay Faults that do Not Need Testing <ul> <li>4.2.1 Robust vs. robust dependent path delay faults</li> <li>4.2.2 Functional irredundant vs. functional redundant path delay faults</li> <li>4.2.3 Path classification based on input sort heuristic</li> <li>4.2.4 Path classification based on using single stuck-at fault tests</li> <li>4.2.5 Primitive vs. non-primitive path delay faults</li> </ul> </li> <li>4.3 Multiple Path Delay Faults and Primitive Faults</li> <li>Summary</li> </ul> | 35<br>36<br>37<br>40<br>41<br>41<br>42<br>44 |  |  |  |  |

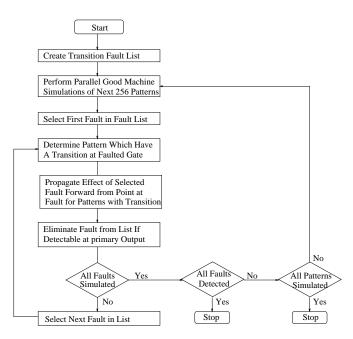

| 5          | DELAY FAULT SIMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47                                           |  |  |  |  |

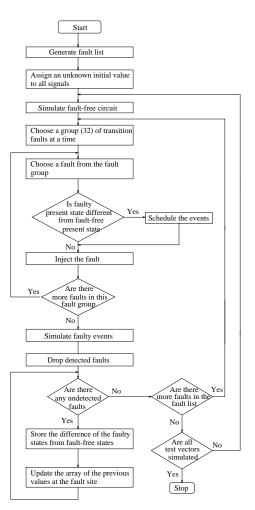

| <b>J</b> . | 5.1 Transition Fault Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                           |  |  |  |  |

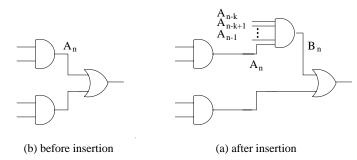

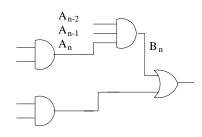

|            | 5.2 Gate Delay Fault Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53                                           |  |  |  |  |

|            | 5.3 Path Delay Fault Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |  |  |  |  |

|            | 5.4 Segment Delay Fault Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57                                           |  |  |  |  |

|            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57                                           |  |  |  |  |

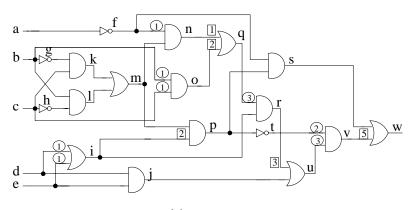

| 6.         | TEST GENERATION FOR PATH DELAY FAULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |  |  |  |  |

|            | 6.1 Robust Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60                                           |  |  |  |  |

|            | 6.2 High Quality Non-Robust Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62                                           |  |  |  |  |

|            | <ul><li>6.2.1 Algorithm for generating non-robust tests with high robustness</li><li>6.3 Validatable Non-Robust Tests</li></ul>                                                                                                                                                                                                                                                                                                                                                                                        | 64                                           |  |  |  |  |

|            | <ul><li>6.3 Validatable Non-Robust Tests</li><li>6.4 High Quality Functional Sensitizable Tests</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                              | 68<br>69                                     |  |  |  |  |

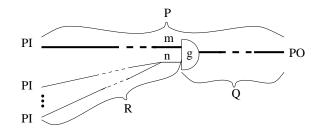

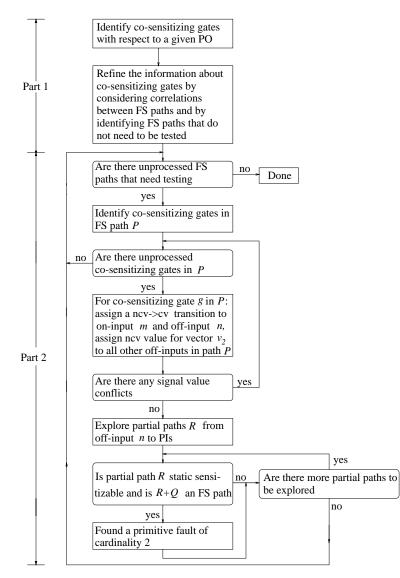

|            | 6.5 Tests for Primitive Faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73                                           |  |  |  |  |

|            | 6.5.1 Co-sensitizing gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74                                           |  |  |  |  |

|            | 6.5.2 Merging gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77                                           |  |  |  |  |

|            | 6.5.3 Identifying FS paths not involved in any primitive fault                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 77                                           |  |  |  |  |

|            | 6.5.4 Primitive faults of cardinality 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78<br>82                                     |  |  |  |  |

|            | Summary 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                              |  |  |  |  |

| 7.         | DESIGN FOR DELAY FAULT TESTABILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85                                           |  |  |  |  |

|            | 7.1 Robust Delay Fault Testability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85                                           |  |  |  |  |

|            | 7.2 Design for Primitive Delay Fault Testability                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 85<br>85                                     |  |  |  |  |

|            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |  |  |  |  |

| 8.         | SYNTHESIS FOR DELAY FAULT TESTABILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87                                           |  |  |  |  |

|            | 8.1 Synthesis for Robust Delay Fault Testability                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 87                                           |  |  |  |  |

|            | 8.2 Synthesis for Primitive Delay Fault Testability                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87                                           |  |  |  |  |

|            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87                                           |  |  |  |  |

| 9.         | CONCLUSIONS AND FUTURE WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 89                                           |  |  |  |  |

| Re         | ferences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91                                           |  |  |  |  |

Preface

This is an example preface. This is an example preface. This is an example preface.

### This is a preface section

This is an example of a preface. This is an example preface. This is an example preface.

Angela Krstić

This book is dedicated to my daughter.

Acknowledgments

text...

## INTRODUCTION Angela Krstić

# 1 TEST APPLICATION SCHEMES FOR VLSI CIRCUITS

Unlike stuck-at fault testing, delay testing is closely tied to the test application strategy. This means that before tests for delay faults are derived it is necessary to know how these tests will be applied to the circuit. The testing strategy depends on the type of the circuit (combinational, scan, non-scan or partial scan sequential circuit) as well as on the speed of the testing equipment. Ordinarily, testing delay defects requires that the test vectors be applied to the circuit at its intended operating speed. However, since high speed testers require huge investments, testers currently used in test facilities are several times slower than the new designs that need to be tested on them. Testing high speed designs on slower testers requires special test application and test generation strategies.

In this chapter, we focus on different test application schemes for combinational and sequential circuits. We describe techniques used for testing scan as well as non-scan designs. Also, we address the issue of testing high speed designs using slow testers and describe some of the currently available solutions to this problem.

#### 1.1 COMBINATIONAL CIRCUITS

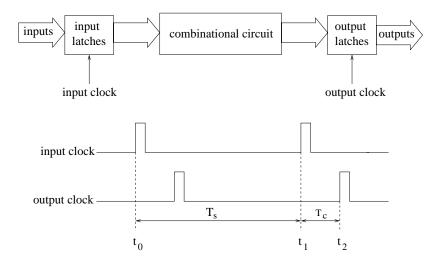

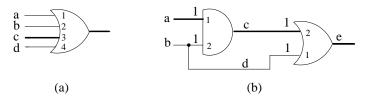

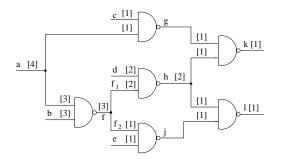

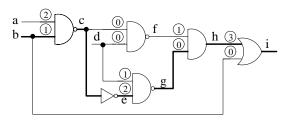

To observe delay defects it is necessary to create and propagate transitions in the circuit. Creating transitions requires application of a vector pair,  $V = \langle v_1, v_2 \rangle$ . The first vector initializes the circuit while the second vector causes the desired transitions. The test application scheme for combinational circuits

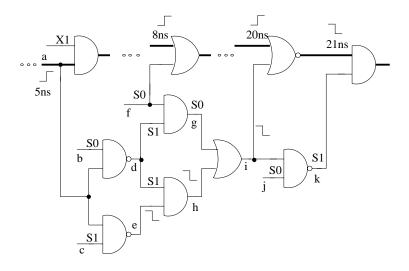

is shown in Figure 1.1. In normal operation, only one clock is used to control the input and output latche (system clock) and its period is  $T_c$ . In testing mode, the input nd output latches are controlled by two different clocks: the input and output clock, respectively. The period of these clocks,  $T_s$ , is assumed t be larger than  $T_c$ . The input and output clocks are skewed by an amount equal to  $T_c$ . The first vector,  $v_1$ , is applied to the primary inputs at time  $t_0$ .

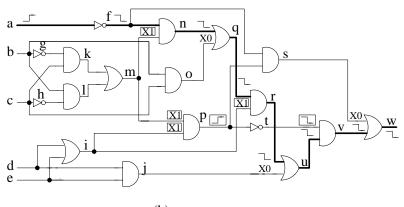

Figure 1.1. Testing scheme for combinational circuits.

The second vector,  $v_2$ , is applied at time  $t_1$ . Time  $T_s = t_1 - t_0$  is assumed to be sufficient for all values in the circuit to stabilize under the first vector. After the second vector is applied, the circuit is allowed to run for one clock cycle until time  $t_2$ , where  $t_2 - t_1 = T_c$ . At time  $t_2$ , the primary output values are observed and compared to a prestored response of a fault-free circuit to determine if there is a defect.

#### 1.2 SEQUENTIAL CIRCUITS

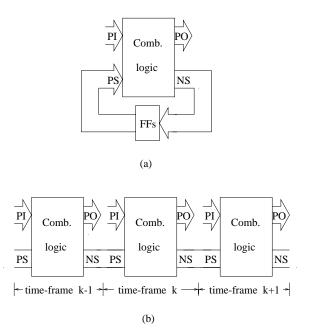

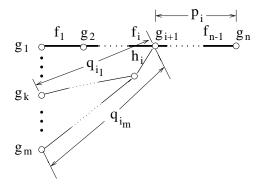

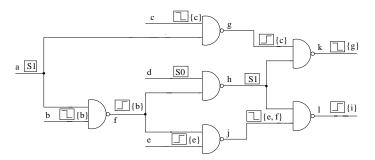

Most of the delay testing research has concentrated on testing combinational circuits. Testing delay faults in sequential circuits is significantly more difficult than testing delay faults in combinational circuits. This is because application of an arbitrary vector pair is not possible to non-scan or standard scan sequential circuits. Figure 1.2(a) illustrates the model of a sequential circuit. Its operation can be represented using an iterative array of the combinational logic (shown in Figure 1.2(b)). Each copy of the combinational logic is called a **time-frame**. The present state (PS) values in time-frame k correspond to the next state (NS) values in time-frame k - 1. In case of a sequential circuit, a vector pair,  $V = \langle v_1, v_2 \rangle$ , can be represented as pair  $V = \langle i_1 + s_1, i_2 + s_2 \rangle$ , where  $i_1, i_2$  are the values of the primary input lines,  $s_1, s_2$  are values of the present

Figure 1.2. Model for sequential circuits.

state lines and symbol "+" denotes concatenation of bit vectors. Therefore, vector  $i_1$  is required to produce  $s_2$  as the next state of the sequential machine.

There are several commonly used testing strategies for sequential circuits: enhanced scan, functional justification and scan shifting for standard scan, slowfast-slow strategy and at-speed strategy for non-scan or partial can designs.

#### 1.2.1 Enhanced scan testing

To solve this problem, Dervisoglu and Strong [17] propose using memory elements that can store two bits of state instead of just one. Such flip-flops are called **enhanced scan flip-flops**. The disadvantages of using enhanced scan flip-flops are high area overhead and long test application time.

#### 1.2.2 Standard scan testing

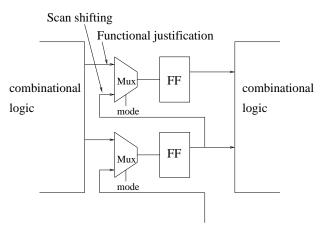

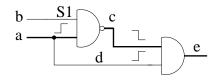

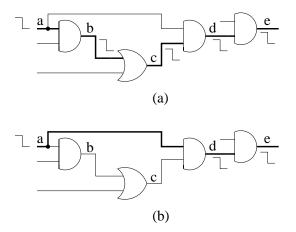

Generating tests for delay faults for standard scan designs corresponds to a two time-frame sequential circuit test generation. In the first time frame, all primary inputs and present state lines are fully controllable. In the second time-frame, only the primary inputs are fully controllable. Testing schemes for standard scan have been proposed in literature [15, 73, 74, 75]. These techniques use **functional justification** (also called **broad-side test** [75]) or **scan shifting** [15] (also called **skewed-load test** [73, 74]) to obtain the second vector. In functional justification, the second vector represents the set of next

state values obtained after the application of the first vector. In scan shifting, the second vector is obtained by shifting the contents of the scan chain by one bit after the application of the first vector. Figure 1.3 illustrates the functional justification and scan shifting concepts.

Figure 1.3. Standard scan design testing schemes.

Cheng *et al.* [15] propose a delay test generation algorithm for standard scan designs. It is modified from a PODEM-based combinational test generator. The modifications involve a two time-frame expansion of the combinational logic of the circuit, and the use of backtracking heuristics tailored to detecting delay faults. The present state values for the second vector are generated using functional justification or scan shifting. A fault that is redundant under scan shifting might be testable under functional justification and vice versa. On the average, the test generation complexity is lower when scan shifting rather than functional justification is used.

The order of flip-flops in the scan chain cannot affect the fault coverage when functional justification is used. However, when scan shifting is applied, the order of flip-flops in the scan chain affects the fault coverage. To find a good order of flip-flops in the scan chain, Cheng et al. [15] first run the test generation algorithm for standard scan designs using functional justification. If the fault is not detectable using functional justification, test generation in enhanced scan mode is tried. The test generator attempts to have as many don't care entries as possible in the present state lines in the second vector of the two vector sequence. Once the test pair,  $\langle v_1, v_2 \rangle = \langle i_1 + s_1, i_2 + s_2 \rangle$ , is generated, a set of constraints on the scan ordering is computed. These constraints, if satisfied, guarantee that  $s_2$  can be obtained by scan shifting of  $v_1$  in standard scan. In general, if the value of flip-flop  $FF_i$  is 0 (1) in  $s_1$  and the value of flip-flop  $FF_i$  is 1(0) in  $s_2$ , then the constraint is that the flip-flop  $FF_i$  cannot be the immediate predecessor of flip-flop  $FF_j$  in the scan chain. If the circuit has n flip-flops, the constraints can be recorded using a quadratic matrix A of size n. Initially all entries in this matrix are set to zero. Given

5

a test vector pair for some target fault, if flip-flop  $FF_i$  is not allowed to be the immediate predecessor of flip-flop  $FF_j$  in the scan chain, then entry  $A_{ij}$  is increased by one. The matrix A is updated after each fault in the fault list is processed, until the fault list becomes empty. The final value  $A_{ij}$  represents the number of faults that will not be detected by scan shifting if flip-flop  $FF_i$  is the predecessor of flip-flop  $FF_j$  under the vector set used to construct the matrix A. The scan ordering is determined such that most of the constraints in matrix A are satisfied. Since a delay fault can have more than one test and only one of the tests is used to construct the matrix A, the fault might be detected even if the constraints in matrix A have not been completely satisfied.

Even with an efficient order of the flip-flops in the scan chain, a certain number of faults that can be detected under enhanced scan design, cannot be detected under standard scan design. To increase the fault coverage, Cheng *at al.* [15] propose **partial enhanced scan** design. In this design methodology, a subset of flip-flops is selected and made enhanced scan. The present state lines of enhanced scan flip-flops are fully controllable in both time-frames in test generation. Given a set of faults that are testable under enhanced scan but are redundant under functional justification or scan shifting scheme with a given ordering of flip-flops, the proposed heuristic attempts to minimize the number of flip-flops to be made enhanced scan in order to achieve a specified fault coverage.

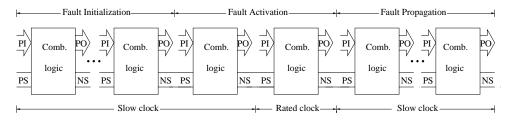

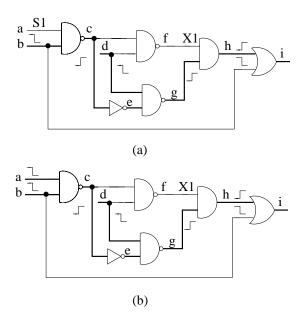

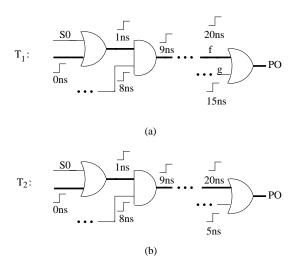

#### 1.2.3 Slow-fast-slow clock testing

Testing a fault in non-scan or partial scan sequential circuits requires a sequence of vectors. These vectors correspond to three different phases of the test generation process: fault initialization, fault activation and fault propagation. Fault initialization sets the signal values to the required values for fault activation. In the fault propagation phase, the fault effect is propagated from a next state line to some primary output. Fault initialization and fault propagation require a test sequence while the fault activation requires a vector pair. The existence of delay defects in the initialization and propagation phases can interfere with activation or the observation of the fault. A common solution is to apply a **slow-fast-slow clock** testing strategy. It assumes that the vectors for initialization and propagation of the fault effect are applied at a slow speed such that the circuit can be considered delay fault-free in these test phases. In the activation phase the first vector is applied under the slow clock while the second vector is applied at the rated speed. Figure 1.4 illustrates the slow-fast-slow testing strategy.

Testing methodologies for non-scan sequential designs using the slow-fastslow scheme have been proposed in [18, 2, 11, 81]. The methodology proposed by Devadas [18] is based on extracting the complete or partial state transition graph. A known reset state is required. Due to the need for extracting the state transition graph, this methodology cannot handle large circuits. Agrawal *et al.* [2] propose inserting a logic block into the sequential circuit netlist for each fault such that testing a delay fault becomes equivalent to testing a certain

Figure 1.4. Slow-fast-slow testing strategy.

stuck-at fault. Chakraborty *et al.* [11] propose a delay test generator based on the iterative logic array model for sequential circuits. It considers two time-frames at a time.

Using a slow clock in fault initialization and fault propagation phases significantly simplifies the test generation for delay faults. However, the need for two clocks (slow and fast) complicates the test application. Testing delay faults in non-scan or partial scan design is further complicated by the fact that it is usually not practical to apply a single fault assumption for delay faults. Therefore, in slow-fast-slow clock testing scheme it could happen that at the end of the fault activation phase more than one flip-flop latches a faulty value. The test generator has to account for this possibility in the fault propagation phase. Chakraborty *et al.* [11] consider different initial conditions for the fault propagation phase.

#### 1.2.4 At-speed testing

At-speed testing strategy assumes that the fault is initialized, activated and propagated under a fast clock. Therefore, delay faults are present in all three phases.

At-speed testing strategies for sequential circuits have been proposed in [64, 13]. Pomeranz *et al.* [64] assume that multiple delay faults can simultaneously be present in the circuit and develop a value system for testing delay faults under these conditions. In their experiments several fast clocks (up to 3) were embedded in sequences of slow clocks. The at-speed test methodology proposed by Cheng [13] uses a single fault assumption.

Some faults that are untestable under the slow-fast-slow clock testing scheme might become testable under the at-speed scheme and vice versa.

### 1.3 TESTING HIGH PERFORMANCE CIRCUITS USING SLOWER TESTERS

Testing a design at its intended operating speed requires high speed testers. High cost of fast testers makes it impossible for the testers to follow the designs in terms of speed increase. The problem of testing high performance circuits without high speed testers has been addressed by a number of researchers [84, 6, 1, 41, 27, 4, 22, 3]. The proposed strategies include tester pin multiplexing [1],

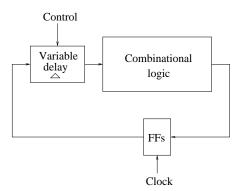

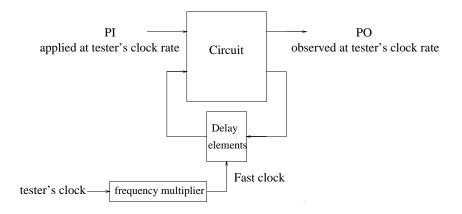

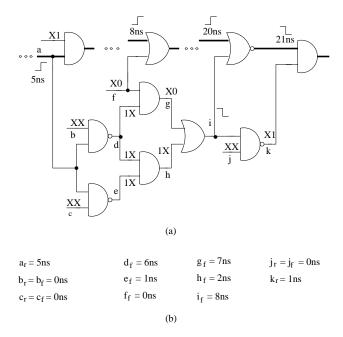

Figure 1.5. Inserting a controllable delay in the combinational logic.

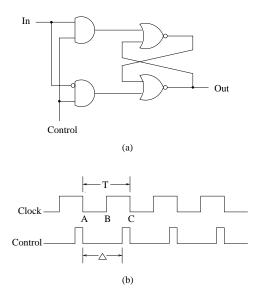

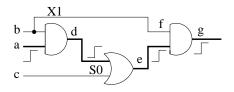

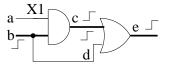

built-in self-test [4], use of a high speed clock and shift registers [41], use of special test fixtures [6], reducing the supply voltage [84, 27], use of on-chip test circuitry for testing high bandwidth memories [22]. The technique proposed by Agrawal *et al.* [3] involve adding extra logic to the combinational logic such that the speed of the circuit in the testing mode becomes slower and comparable to the speed of testers. The amount of the added delay can be controlled by a test input signal. Figure 1.5 illustrates the concept. The extra logic for inserting

Figure 1.6. A controlled delay element and a waveform applied to the control input.

the variable delay should: (1) be controllable, (2) have a minimum normal

mode delay, (3) be testable and (4) use minimum logic. The following example describes one possible implementation of such logic.

EXAMPLE 1.1 Consider the circuit in Figure 1.6(a) [3]. When the control input is set to 1, the input signal propagates to the output. When the control input is 0, the output holds its value. During normal operation, the control input is held at 1. If single clock master-slave flip-flops are assumed and the clock waveform is as shown in Figure 1.6(b), the falling edge A is the time when the data is transferred from the master to slave flip-flop and the data stored in the slave flip-flop is applied to the combinational logic. The new data stored in the slave flip-flop will stay there until the next falling edge C. The rising edge Bopens the master flip-flop to the input data. The time between the two falling edges (A and C) represents the clock period T. Figure 1.6(b) also shows the waveform for the control signal for the inserted logic. At the falling edge A of the clock, control signal drops to 0 and blocks the application of the data from the slave flip-flop to the combinational logic. After a delay  $\Delta$ , the control signal rises to 1 and thus, allows the value from the slave flip-flop to be applied to the combinational logic. From Figure 1.6(b) it is clear that if T represents the clock period of the tester, then the clock period of the circuit can at most be  $T_{rated} = T - \Delta$ . In the test mode, delay  $\Delta$  can be varied by changing the pulse width of the waveform.

The use of slow-fast-slow and at-speed testing schemes for testing high performance designs on slow testers has been discused by Krstić *et al.* [46]. They assume that the speed of the circuit is k (k is a positive integer) times higher than the speed of the tester and that an internal fast clock matching the speed of the circuit is available. If there is no fast clock available on the tester, the fast clock can be generated using frequency multiplier and the tester's clock.

#### 1.3.1 Slow-fast-slow testing strategy on slow testers

The slow-fast-slow testing scheme can, under certain constraints, be used to test high performance circuits on low speed testers. In this scheme, the testable set of faults is affected by the presence or absence of latches on primary outputs. This is because to observe a fault, after activation, it has to be propagated to some primary output.

DEFINITION 1.1 Faults that in the activation time-frame can be propagated only to a primary output are called **PO-logic faults**.

DEFINITION 1.2 Faults that in the activation time-frame can be propagated to either a primary output or to a next state line and faults that in the activation time-frame can be propagated only to a next state line are called *NS-logic faults*.

Next, we consider the use of slow-fast-slow scheme on slow testers for testing non-scan, scan and partial scan designs.

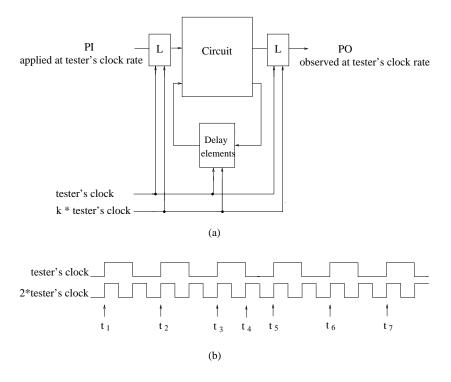

**Testing non-scan designs.** The test application scheme for non-scan designs with latched PI/PO is shown in Figure 1.7(a). The primary inputs can be latched but it is not essential. The primary inputs are applied and the primary outputs are observed at the tester's speed. The tester's clock is also used in the slow phases (fault initialization and fault propagation). The tester's clock is assumed to be slow enough for the circuit to be fault-free in these phases. Fault activation is performed with a fast clock.

EXAMPLE 1.2 Consider the waveform in Figure 1.7(b). It illustrates the case when when the tester's clock is 2 times slower than the operating speed of the circuit under test, i.e., k = 2. Also, it is assumed that the test sequence for the target fault consists of two initialization vectors  $(v_1 \text{ and } v_2)$ , one activation vector  $(v_3)$  and two propagation vectors  $(v_4 \text{ and } v_5)$ . Initialization vectors,  $v_1$ and  $v_2$  are applied at times  $t_1$  and  $t_2$ , respectively. After the application of the activation vector at time  $t_3$ , the values of the primary outputs and next states are latched at time  $t_4$ . Next, the propagation vectors  $v_4$  and  $v_5$  are applied at times  $t_5$  and  $t_6$ , respectively. Finally, at time  $t_7$ , the primary outputs are observed.

Figure 1.7. Non-scan designs with latched PI/PO.

Since the primary outputs can be latched at the end of the activation phase, this methodology can test both NS-logic and PO-logic faults.

When the primary outputs are not latched, PO-logic faults might not be testable on a slow tester using slow-fast-slow testing scheme. Only faults that are larger than a certain size can be tested. For example, PO-logic faults in the circuit in Figure 1.7(a) have to be larger than  $t_5 - t_4$  to be testable.

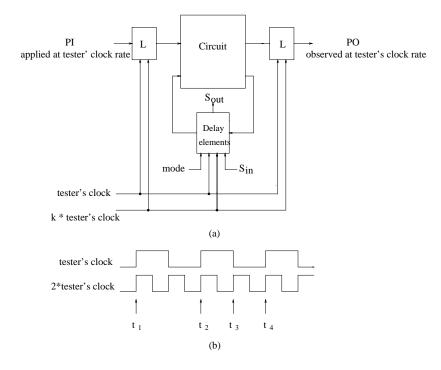

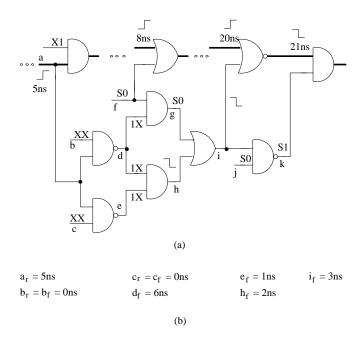

**Testing Scan Designs.** Test application scheme that allows testing high speed scan designs on a low speed tester is illustrated in Figure 1.8(a). The tester's clock is used for applying the primary inputs, for the scan-in operation as well as for observation of the primary outputs and next state values, i.e., scan-out operation. The fast clock is used for latching the values into primary outputs and next states.

EXAMPLE 1.3 The waveform in Figure 1.8(b) illustrates the case when k = 2. First the present state values,  $v_1$ , are scanned into the registers. Next, vector  $v_1 = (i_1 + s_1)$  is applied at time  $t_1$ . If standard scan is used, the state values  $s_2$  of the second vector can be obtained through functional justification [15]. The second vector,  $v_2 = (i_2 + s_2)$ , is applied at time  $t_2$ . Time  $t_2 - t_1$  is assumed to be sufficient for the signal values to settle to their final values after the application of vector  $v_1$  and before application of  $v_2$ . Next, one fast clock cycle is applied and at time  $t_3$ , the values of the primary outputs and next states are latched. At time  $t_4$ , the primary outputs can be observed and the scan-out operation can start. Then, the same cycle repeats for the next test.

Since the primary outputs can be latched after the application of the fast clock, both PO-logic and NS-logic faults can be tested using this scheme. However, if the scan circuit in Figure 1.8(a) does not have latches at the primary outputs, from the waveform in Figure 1.8(b) we get that PO-logic faults have to be larger than  $t_4 - t_3$  in order to be detectable.

**Testing Partial Scan Designs.** Testing scheme for partial scan designs represents a combination of the schemes described for non-scan and scan designs. The testing strategy depends on the target fault. For faults that can be tested through paths between the non-scan flip-flops, faults between non-scan flip-flops and POs and faults between PIs and non-scan flip-flops, the testing process is similar to the process described for faults in non-scan designs. It consists of initialization, activation and propagation phase. However, since some of the memory elements are scanned, the initialization and propagation phases might be shorter than in the non-scan case. For faults that can be tested through paths between PIs and scanned flip-flops, the testing strategy is the same as the one described for scan designs.

#### 1.3.2 At-speed testing strategy on slow testers

Conventional at-speed testing strategies for sequential circuits [64, 13] assume that the inputs are applied and the outputs are observed at the circuit's rated

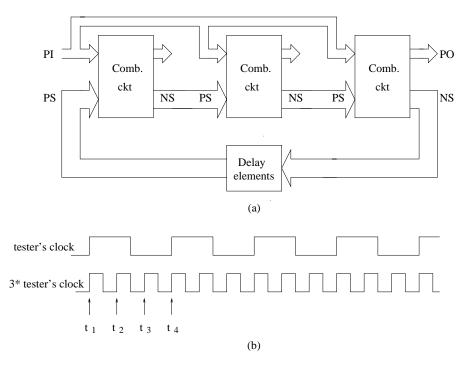

**Figure 1.8.** Scan designs with latched PI/PO.

speed. This is impossible to do on a low speed tester. Krstić *et al.* [46] propose an at-speed methodology that accommodates the slow speed of the tester. Figure 1.9 illustrates the proposed at-speed scheme. The inputs to the circuit are applied and the outputs are observed at the slow tester's rate. Using the internal fast clock makes the circuit go through k states between applying the inputs and observing the outputs. This is equivalent to saying that the same set of primary input values are applied for k clock cycles and that the primary outputs are observed only at the end of each k-th cycle. Since the circuit runs at-speed between each application of inputs and observation of outputs, delay faults are constantly present in the circuit.

EXAMPLE 1.4 Figure 1.10(a) illustrates the proposed at-speed testing scheme for k = 3. The same set of primary input values is applied for three fast clock cycles and the primary outputs are only observed after the third cycle. The delay elements are clocked with the fast clock and the circuit passes through three different states before the application of the next set of primary inputs.

Since the observation of the outputs is performed at the tester's speed, the existence or non-existence of latches at the primary outputs does not affect which faults can be tested using this at-speed scheme. This means that the

Figure 1.9. At-speed testing strategy for slow testers.

**Figure 1.10.** At-speed testing scheme for k = 3.

proposed at-speed scheme can be used to test PO-logic faults that cannot be tested using slow-fast-slow scheme.

Next, we consider the application of the at-speed testing scheme to non-scan, scan and partial scan designs.

**Testing Non-Scan Designs.** Let the design in Figure 1.10(a) be a non-scan design and consider the waveform shown in Figure 1.10(b). At time  $t_1$ , vector  $v_1 = (i_1 + s_1)$  is applied to the circuit. Next, at time  $t_2$ , the primary input values stay unchanged but the state values have changed. Therefore, at time  $t_2$ , vector  $v_2 = (i_1 + s_2)$  is applied to the circuit. Similarly, at time  $t_3$ , vector  $v_3 = (i_1 + s_3)$  is applied. Finally, at time  $t_4$ , the primary outputs can be observed. A new vector,  $v_4 = (i_2 + s_4)$ , is applied to the circuit at time  $t_4$  and the cycle repeats. In this scheme, if the test sequence contains n test vectors, where n is a positive integer, the circuit actually changes  $k \times n$  states. For example, the circuit in Figure 1.10(a) must go through 3 or 6 or 9, ... states. Therefore, the test generation process for at-speed schemes that assume fast testers.

**Testing Scan Designs.** Let the design in Figure 1.10(a) be a scan design and consider the waveform shown in Figure 1.10(b). The application of primary inputs, scan-in, scan-out and observation of the primary output values are performed at the tester's speed. However, between the scan-in and scan-out operations, the circuit is allowed to run with the fast clock and it goes through three states while the primary inputs are kept constant. At time  $t_1$ , the first set of state values,  $s_1$ , is assumed to be already scanned-in and  $i_1$  is applied at the primary inputs. The state values for the second and third vector,  $v_2 =$  $(i_1 + s_2)$  and  $v_3 = (i_1 + s_3)$ , are obtained through functional justification and these vectors are applied at times  $t_2$  and  $t_3$ , respectively. At time  $t_4$ , the values of the primary outputs are observed and the scan-out operation starts. The test sequence for scan designs contains k vectors.

**Testing Partial Scan Designs.** As with slow-fast-slow scheme, the at-speed testing strategy for partial scan designs can be described as a combination of testing strategies for scan and non-scan designs (depending on the target fault).

Since in this at-speed testing strategy the primary outputs are observed only after each k-th cycle, the signal observability is smaller than if the primary outputs are observed after each cycle. Also, since the primary inputs are kept unchanged for k clock cycles, the controllability of the signals is negatively affected as well. This can lead to lower fault coverage than if a high speed tester was available. Therefore, the described at-speed technique should not be used as a stand-alone technique. Instead, it can be combined with the slowfast-slow testing strategy to obtain higher overall fault coverage. In the case when there are no latches on the primary outputs, the at-speed technique can be used to test PO-logic faults that would stay untestable under slow-fast-slow strategy. In addition, some NS-logic faults might also be untestable by a slowfast-slow scheme but testable by the at-speed scheme. The proposed at-speed scheme can be used to detect them as well. Also, there exist faults that can be tested by both slow-fast-slow testing strategy and by the at-speed strategy. If these two strategies require that the circuit passes through a comparable

number of states when testing a given fault, the at-speed scheme would clearly be superior in terms of the testing time.

#### Summary

Test application strategy is integral part of delay test generation. This is especially true for testing sequential designs for which several different strategies exist. Enhanced vs. standard scan schemes show the trade-offs between the overhead in area and test application time versus fault coverage. Enhaced scan requires high area and test application time overhead but it also results in a higher fault coverage than standard scan techniques. In slow-fast-slow testing scheme, the assumption that the circuit is fault-free in the fault initialization and propagation phases greatly reduces the complexity of test generation but it complicates the test application process (when compared to the at-speed testing scheme).

An important factor in delay fault test generation is also the tester's speed. The speed of the testers usually lags behind the speed of the new designs. Therefore, developing new techniques that would allow testing high speed designs on slower testers is of great practical importance.

# 2 DELAY FAULT MODELS

The focus of this chapter is on the ways to model delay faults. Five delay fault models are considered: transition fault model, gate delay fault model, path delay fault model, segment delay fault model and line delay fault model. It is assumed that each gate can have an arbitrary fall (rise) delay from each input to the output pin. Also, the interconnects are assumed to have arbitrary rise (fall) delays. Since the gate pin-to-pin delays and the interconnect delays can be combined together, we will only talk about delays of gates. Transition, gate and line delay models are used for representing delay faults lumped at gates while the path and segment delay model address faults that are distributed over several gates. The advantages and disadvantages of each model are discussed.

#### 2.1 TRANSITION FAULT MODEL

**Transition fault model** [13, 49, 76, 86] assumes that the delay fault affects only one gate in the circuit. There are two transition faults associated with each gate: a slow-to-rise fault and a slow-to-fall fault. It is assumed that in the fault-free circuit each gate has some nominal delay. Delay faults result in an increase or decrease of this delay. (Thoughout this book only delay faults caused by an increase of the delay will be considered.) Under transition fault model, the extra delay caused by the fault is assumed to be large enough to prevent the transition from reaching any primary output at the time of observation. In other words, the delay fault can be observed independent of whether the

transition propagates through a long or a short path to any primary output. Therefore, this model is also called *gross delay fault model* [60]. In addition to being a model for delay faults, transition fault model is also used as a logic model for transistor stuck-open faults in CMOS circuits [83]. CMOS transistor stuck-open faults can be treated as faults that either suppress or delay the occurrence of certain transitions. In practice, the extra delay caused by a stuckopen fault depends on the electrical characteristics of the defective component.

To detect a transition fault in a combinational circuit it is necessary to apply two input vectors,  $V = \langle v_1, v_2 \rangle$ . The first vector,  $v_1$ , initializes the circuit, while the second vector,  $v_2$ , activates the fault and propagates its effect to some primary output. During the application of the second vector the fault behaves as a stuck-at fault and vector  $v_2$  can be found using stuck-at fault test generation tools. For example, for testing a slow-to-rise transition, the first pattern initializes the fault site to 0, and the second pattern is a test for stuck-at-0 fault at the fault site. A transition fault is considered detected if a transition occurs at the fault site and a sensitized path extends from the fault site to some primary output.

The fault equivalence rules for transition faults are more restrictive than those for stuck-at faults [86]. This is because, as mentioned above, testing a transition fault requires more than one vector. Only two rules can be applied for fault equivalence collapsing for transition faults: (1) if a gate has one input, then the input transition faults are equivalent to the output transition faults, and (2) if a gate has only one fanout, then the output transition faults are equivalent to the input transition faults on the fanout gate. As a result, the number of collapsed transition faults for a given circuit is larger than the number of collapsed stuck-at faults.

The main advantage of the transition fault model is that the number of faults in the circuit is linear in terms of the number of gates. Also, the stuck-at fault test generation and fault simulation tools can be easily modified for handling transition faults. On the other hand, the expectation that the delay fault is large enough for the effect to propagate through any path passing through the fault site might not be realistic because short paths may have a large slack. The assumption that the delay fault only affects one gate in the circuit might not be realistic, either. A delay defect can affect more than one gate and even though none of the individual delay faults is large enough to affect the performance of the circuit, several faults can together result in a performance degradation. For practical simplicity, the transition fault model is frequently used as a qualitative delay model and circuit delays are not considered in deriving tests.

**Transition fault model for sequential circuits.** The transition fault model described above cannot be used for sequential circuits if the clock is applied at the rated speed because it does not take into account the fault size. We now discuss a transition fault model [13] that is suitable for the at-speed test application scheme.

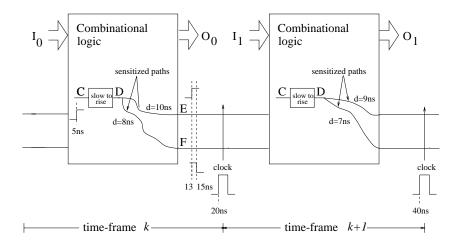

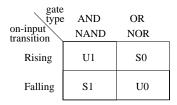

Figure 2.1. Faults of different size result in different next states.

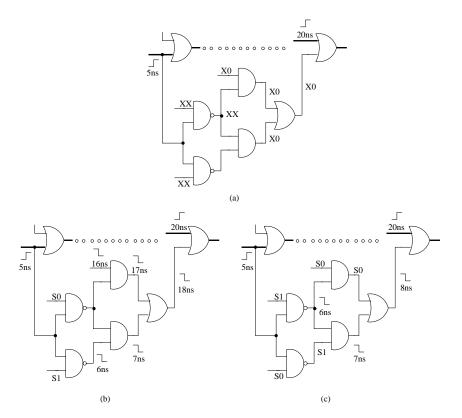

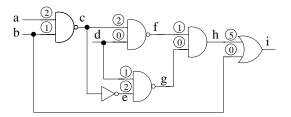

The transition fault model for a sequential circuit [13] is characterized by the fault site, the fault type and the fault size. As before, the fault type is slow-to-rise or slow-to-fall transition. The fault size represents the amount of extra delay caused by the defect. In sequential circuits, different fault sizes will result in different faulty next states.

EXAMPLE 2.1 Consider the circuit in Figure 2.1. Figure 2.1 shows two timeframes of the given sequential circuit. It is assumed that input vectors are applied at the rated speed. The clock pulse for latching the next state is applied before the next input vector is applied. Suppose there is a slow-to-rise fault between the signal C and signal D. The clock interval is 20 nanoseconds (ns). The inputs are applied at 0ns (reference time) for time-frame k and a rising transition occurs at signal C at 5ns. There are two sensitized paths from Cto the next state signals, E and F. The propagation delays of the transitions along these two paths are 10 and 8 ns, respectively. The transitions at E and F for the fault free-circuit and the times at which they occur are shown in the figure. If the fault size of the slow-to-rise fault at C is less than 5ns, the next state of the faulty circuit will be the same as that of the fault-free circuit, i.e., (E, F) = (1, 0). If the fault size is greater than 5ns but less than 7ns, flip-flop E will catch the fault effect but flip-flop F will not (when the clock is applied at 20ns). The faulty next state will be (E, F) = (0, 0). If the fault size is greater than 7ns, the faulty next state will be (E, F) = (0, 1). The faulty next state, along with the next input vector, will produce a new logic value at each signal in time frame k + 1. Next, let the longest and shortest sensitized paths from C to any next state signal in time-frame k+1 have delays of 9ns and 7ns, respectively. If the value at C in time-frame k+1 is a logic 1 and if the fault size is in the range of (7ns, 26ns), the value at signal D in time frame k+1 will be 1. The effects of the delayed transition will be stabilized at the next state signals in time-frame k + 1 before the following clock pulse is applied at 40ns.

On the other hand, if the new value at C is a logic 0, regardless of the fault size, the delayed transition will be completely suppressed and the value at D in time-frame k + 1 will be 0. If the value at C in time-frame k + 1 is a logic 1 and if the fault size is in the range of (26ns, 28ns), the effects of the delayed transition will be propagated to signal E and stabilized before the next clock pulse is applied. However, the next state signal F will not catch the fault effect in this case.

Clearly, it is not possible to guarantee the detection of a transition fault in a sequential circuit under the at-speed test application scheme without considering the size of the fault. Different fault sizes result in completely different circuit behaviors. However, the computation costs of dividing the fault sizes into hundreds of fine-grained ranges and simulating them are prohibitive. This problem can be solved by dividing the fault using units of clock cycles [13].

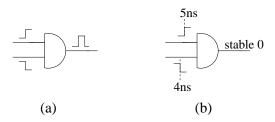

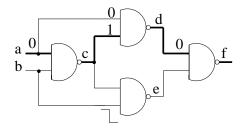

Figure 2.2. Advantage of considering circuit timing

#### 2.2 GATE DELAY FAULT MODEL

**Gate delay fault model** [9, 33, 34, 35, 69, 70] assumes that the delay fault is lumped at one gate in the circuit. However, unlike the transition model, gate delay fault model does not assume that the increased delay will affect the performance independent of the propagation path through the fault site. It is assumed that long paths through the fault site might cause performance degradation. Gate delay fault model is a quantitative model since it takes into account the circuit delays. The delays of the gates are represented as intervals. The gate delay fault model has the following characteristics [35]:

- (1) The delay through a gate depends on the logic values applied to the gate.

- (2) Multiple copies of a gate have different delays due to manufacturing variations.

- (3) A gate has some inertia in responding to changes at its inputs. Transients of short duration at the gate inputs get filtered out from the response at the output.

Taking the timing into consideration when deriving tests for gate delay faults allows application of some tests that would otherwise not be considered.

EXAMPLE 2.2 Consider the AND gate shown in Figure 2.2. If no information about the delays in the circuit is available, it might be assumed that there is a static hazard at the output of the AND gate, as shown in Figure 2.2(a). This static hazard might prevent the propagation of some target fault elsewhere in the circuit. However, if the information about delays is given and the arrival times of the transitions at the inputs to the AND gate are as shown in Figure 2.2(b), the output will clearly have a stable 0 value, which may be favorable for the propagation of the target fault effect.

To determine the ability of a test to detect a gate delay defect it is necessary to specify the delay size of the fault. Methods for computing the smallest delay fault size (detection threshold) guaranteed to be detected by some test have been reported in the literature [33, 34, 69, 70].

The limitations of the gate delay fault model are similar to those for the transition fault model. Namely, because of the single gate delay fault assumption a test may fail to detect delay faults that are result of the sum of several small delay defects. The main advantage of this model is that the number of faults is linear in the number of gates in the circuit.

#### 2.3 PATH DELAY FAULT MODEL

Under **path delay fault model** [79] a combinational circuit is considered faulty if the delay of any of its paths exceeds a specified limit. A path is defined as an ordered set of gates  $\{g_0, g_1, \ldots, g_n\}$ , where  $g_0$  and  $g_n$  are a primary input and primary output, respectively. Also, gate  $g_i$  is an input to gate  $g_{i+1}$   $(0 \le i \le n-1)$ . A delay defect on a path can be observed by propagating a transition through the path. Therefore, a path delay fault specification consists of a physical path and a transition that will be applied at the beginning of the path. The delay or length of the path represents the sum of the delays of the gates and interconnections on that path.

Tests for the path delay fault model can detect small distributed delay defects caused by statistical process variations. A major limitation of this fault model is that the number of paths in the circuit can be very large (possibly exponential in the number of gates). For this reason testing all path delay faults in the circuit is not practical. Two strategies are commonly used for selecting the set of path delay faults for testing. One is to select a minimal set of paths such that for each signal s in the circuit the longest path containing s is selected for testing [50, 55, 54]. The other is to select all paths with expected delays greater than the specified threshold. The reason behind selecting the longest paths is that the delay defects on shorter paths might not be large enough to affect the circuit performance. Also, if the defects on short paths are large and could affect the performance, one expects that such defects would be detected by other tests (e.g., at-speed tests and gate delay tests) that precede the path delay fault testing. This strategy might work for circuits whose paths have very different delays so that there is a small percentage of long paths. However, often in performance optimized designs almost all paths have long delays and in these circuits not even all longest paths can be tested [61]. Therefore, even after

path delay fault testing, the temporal correctness of the circuit under test often cannot be guaranteed. The problem can be alleviated by developing techniques for resynthesizing the circuits such that the path count is reduced [44, 68].

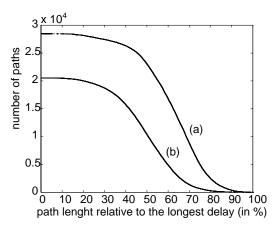

EXAMPLE 2.3 Consider the path distribution for some circuit to be as shown in Figure 2.3 [44]. Horizontal axis represents the path length relative to the longest sensitizable path delay in the circuit. Vertical axis shows the number of paths whose delay is longer than the corresponding percentage of the critical path length. Let curve (a) represent the path distribution in the original circuit and curve (b) represent the path distribution in the resynthesized circuit such that the path count is reduced. Let us also assume that it is possible to test 5000 paths for delay defects. Selecting 5000 paths in the original circuit means that all paths longer than 75% of longest sensitizable path length can be checked for delay faults. On the other hand, selecting 5000 paths in the resynthesized circuit means that all paths longer than 59% of the critical path length can be checked. Therefore, the tests derived for the resynthesized circuit will be able to cover a larger portion of all possible path delay faults.

Figure 2.3. Path distributions for a circuit (a) before and (b) after resynthesis for path count reduction.

Additional problems with the use of the path delay fault are: (1) Tests that guarantee that the given path will not affect the performance of the circuit can be generated using reasonable resources only for a small set of paths in the circuit. For most circuits, there exists a large number of paths that can impact the performance of the circuit but these paths cannot be easily tested. Classification of path delay faults based on their testability characteristics is considered in Chapter 4. (2) Most path delay fault testing research has concentrated on testing combinational circuits. Extending these techniques to non-scan or partial scan designs is not straightforward.

#### 2.4 SEGMENT DELAY FAULT MODEL

Segment delay fault model [29, 30] represents a trade-off between the transition delay fault model and path delay fault model. The assumption in this model is that the delay defect affects several gates in a local region of occurrence. Also, it is assumed that a segment delay fault is large enough to cause a delay fault on all paths that include the segment. The length of the segment, L, can be anywhere from 1 to  $L_{max}$ , where  $L_{max}$  represents the number of gates in the longest path in the circuit. The fault list consists of all segments of length L and all paths whose length is less than L. When L = 1, this model reduces to the transition fault model. When  $L = L_{max}$ , the segment delay fault model is equivalent to the path delay fault model. The idea of using the segment delay model is to combine the advantages of the transition and path delay fault models while avoiding their limitations. Since the number of segment delay faults for a given L can be much smaller than the number of all paths in the circuit, the explosion of the number of faults can be avoided. Also, the assumption that the fault is distributed over several segments is more realistic than the transition fault assumption about the lumped delay fault at one segment. In addition, in practice, many segments are testable while the entire paths containing those segments may not be testable.

The length of the segment can be decided on the basis of available statistics about manufacturing defects. All segments of a given length can be counted and identified using the method in [29].

#### 2.5 LINE DELAY FAULT MODEL

Line delay fault model [54] tests a rising (falling) delay fault on a given signal (line) in the circuit. The fault is propagated through the longest *sensitizable* path passing through the given line. Similar to transition and gate delay fault models, line delay fault model assumes a single delay fault. Therefore, the number of faults equals twice the number of lines in the circuit. Sensitizing the longest path through the target line allows detecting the delay fault of the smallest size on the target line. In general, a test will cover several line delay faults. Therefore, this fault model can also detect some distributed delay defects on the propagation paths. However, since only one propagation path through each line is considered, this model can fail to detect some distributed defects [53].

#### Summary

Fault models represent an approximation of the effects that defects produce on the behavior of the circuit. An ideal model should provide a high confidence level that faulty circuits will be detected. The test generation process for such a fault model should allow handling of very large designs with reasonable amount of computing resources. Detecting timing defects requires models other than the well known stuck-at fault model. Several different delay fault models have been proposed in literature. Each of these models has its advantages and

disadvantages. The main characteristics of the delay fault models are shown in Table 2.1. Path delay fault model is usually considered to be closest to the ideal

| Delay fault<br>model | number of<br>faults w.r.t.<br>number of gates | faults that can be tested                               | $size  of \ detectable \ faults$ | $test \\ generation$                                          |

|----------------------|-----------------------------------------------|---------------------------------------------------------|----------------------------------|---------------------------------------------------------------|

| transition           | linear                                        | lumped at<br>gate                                       | large                            | modified<br>stuck-at<br>ATPG                                  |

| gate                 | linear                                        | lumped at<br>gate                                       | larger than<br>threshold         | takes timing<br>into account                                  |

| path                 | exponential (worst case)                      | distributed along paths                                 | small to<br>large                | hard                                                          |

| segment              | linear to<br>exponential                      | distributed<br>along segments                           | small to<br>large                | depends on the<br>segment length                              |

| line                 | linear                                        | lumped at gate<br>or distributed<br>along certain paths | small to<br>large                | requires finding<br>longest sensitizable<br>path through line |

Table 2.1.

Comparison of different delay fault models.

model for delay defects. However, testing all path delay faults that can affect the performance of the circuit is impractical. Currently used path delay fault model is oversimplified for deep submicron devices for which the interconnect and cell delays are highly pattern dependent. Developing a more accurate fault model and selection of critical paths in new designs that are highly sensitive to process variations, circuit defects and coupling effects are important research problems for the future.

# 3 MOTIVATIONS FOR DELAY TESTING

This chapter discusses the motivations for subjecting a design to delay testing. The conclusions of several case studies carried out by various research groups are presented.

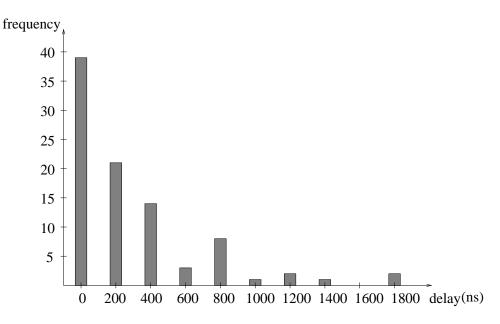

Research and experiments have shown that for high design quality requirements it is not sufficient to test a design only for stuck-at faults [8, 56, 82, 57]. There exist some faults that can only be detected if multiple test strategies are used. For example, an IBM experiment has shown that "randomly occuring gross delay defects can allow chips to pass full stuck-at fault testing at both wafer and module levels, but cause them to fail when operated at system speeds" [8]. In the experiment 60,000 dc good modules representing chips from the same IBM computer system have been subjected to delay testing. The modules were designed using CMOS standard cell/gate array and the experiment was performed for transition fault model. The test fault coverage was 75%. There were 97 dc good modules that have failed the delay testing, i.e., that had gross delay defects but were not detected with stuck-at fault testing. The histogram in Figure 3.1 [8] shows the distribution of fault sizes for 91 out of 97 modules that have failed the delay test. The clock cycle time was 120ns. In this experiment, 42.86% of the gross delay defects had size between 1 and 200 ns, while 65.93% of the delay defects was between 1 and 200ns. The experiment has clearly demonstrated the benefit of delay testing.

A possible cost effective strategy for delay testing would include:

Figure 3.1. Fault size distribution in an IBM experiment.

- use of functional vectors that could be applied at-speed and should catch some delay defects. Functional vectors should be evaluated for transition fault coverage.

- application of tests for undetected transition faults

- application of tests for long path delay faults.

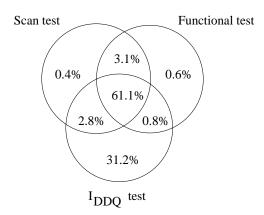

Several recent studies have investigated detection of timing defects in CMOS circuits by  $I_{DDQ}$  tests [56, 82, 57]. The experiment performed by Maxwell *et al.* has shown that  $I_{DDQ}$  testing can detect some delay defects. However, there exist some delay defects (distributed small delay defects caused by process valation, elevated series resistance in interconnects, elevated inteconnect capacitance) that can only be detected by delay testing. For example, the experiment described in [56] has tested a sample of 26,415 die. There were three types of tests applied: functional, scan and  $I_{DDQ}$ . Testing has identified 4,349 devices as faulty. Figure 3.2 [56] illustrates the distribution of the failing die in each test class. A total of 21 parts passed scan and low speed (2 MHz) functional tests but failed at-speed (20 and 32 MHz) functional tests. Only 10 out of 21 delay defective parts was detected by  $I_{DDQ}$  tests. Therefore, this study has suggested a testing strategy that combines high static stuck-at coverage,  $I_{DDQ}$  tests and delay tests.

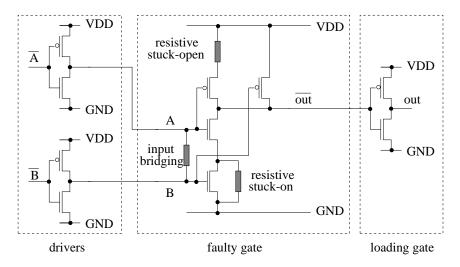

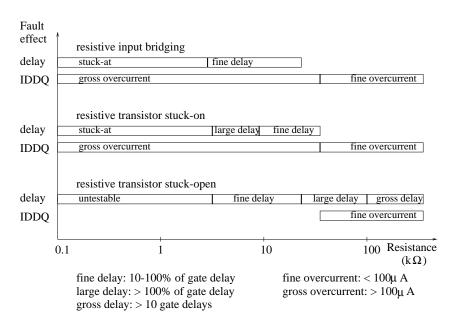

The delay and overcurrent effects of resistive faults have been investigated by Vierhaus *et al.* [82]. Detailed simulations of resistive stuck-on, stuck-open and bridging faults have been performed for typical CMOS circuits. Figure 3.3

Figure 3.2. Distribution of failing die.

illustrates the simulated faults in a 2-input CMOS NAND gate. The summary

Figure 3.3. Considered resistive faults in 2-input CMOS AND gate.

of the delay and overcurrent effects for the 2-input AND gate in 1.5 - 2 micron CMOS technology is shown in Figure 3.4. For example, for resistive transistor stuck-open faults for resistor values between 5 and 70 k $\omega$ , the defects can be detected only by delay testing (overcurrent testing would not detect these faults).

#### Summary

Figure 3.4. Delay and overcurrent effects for resistive faults in a 2-input CMOS AND gate.

# 4 PATH DELAY FAULT CLASSIFICATION

This chapter is devoted to a discussion on the classification of path delay faults. Paths are classified according to their testability characteristics. A given path delay fault can be tested by many different tests. Unlike a stuck-at fault for which all tests have the same quality (fault is certainly detected by the test), in path delay fault testing different tests for a given fault have different levels of quality (probability of detection). For example, some tests can guarantee detection of a fault while others can detect the fault only under restricted conditions. Not every path can be tested with a highest quality test. This is because higher quality path delay fault tests require more stringent conditions for path sensitization. To ensure the highest quality of path delay fault testing, each path delay should be tested under the most stringent sensitization criterion for which a test exists. Given various path sensitization criteria, paths are generally classified into several classes: robust, non-robust, functional sensitizable and functional unsensitizable.

Some path delay faults do not need to be tested to guarantee the performance of the circuit. This is because these path delay faults can never independently affect the performance. There are many different ways to partition the set of paths into the set that needs to be tested and the set that does not need to be tested.

This chapter describes two criteria for classifying path delay faults. The first one is based on the path sensitization and the second is based on whether

or not the given path needs to be tested to guarantee the performance of the circuit. Both single and multiple path delay faults are considered.

## 4.1 SENSITIZATION CRITERIA

Testing delay faults requires two vector patterns. Accordingly, path sensitization criteria are defined with respect to two vectors. This section addresses the sensitization of single path delay faults. Multiple path delay faults are addressed in Section 4.3.

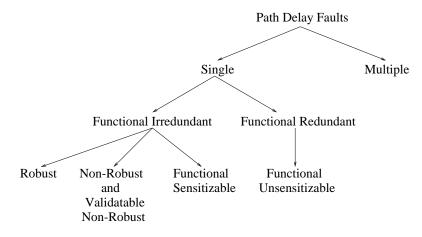

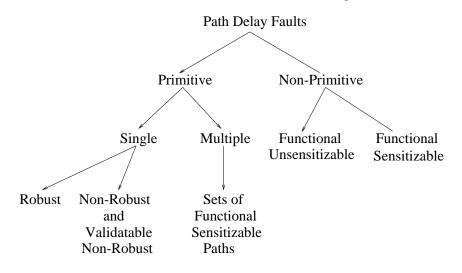

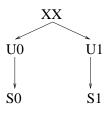

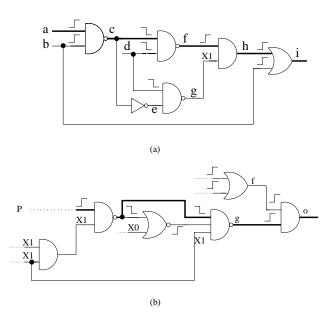

Figure 4.1. Path delay fault classification.

There exist several classes of path delay faults according to the sensitization criteria: robust, non-robust, validatable non-robust, functional sensitizable and functional unsensitizable faults. These classes have different testability characteristics based on the specific fault detection conditions. The robust, nonrobust, validatable non-robust and functional sensitizable faults can affect the performance of the circuit and they are together called functional irredundant faults. Functional unsensitizable faults, also called functional redundant faults, can never independently determine the performance and they do not have to be tested. This section considers only functional irredundant faults, while functional unsensitizable faults will be addressed in Section 4.2. The path delay fault classification used in this book is illustrated in Figure 4.1. Note that most of the literature on path delay faults considers the non-robust set as a superset of the robust set of paths and the functional sensitizable set as a superet of non-robust testable set. However, in this book the set of robust testable, non-robust testable and functional sensitizable path delay faults are considered to be disjoint. The terminology that will be used in the rest of the book is given next.

**Terminology.** An input to a gate is said to have a **controlling value** (denoted as cv) if it determines the value of the gate output regardless of the values